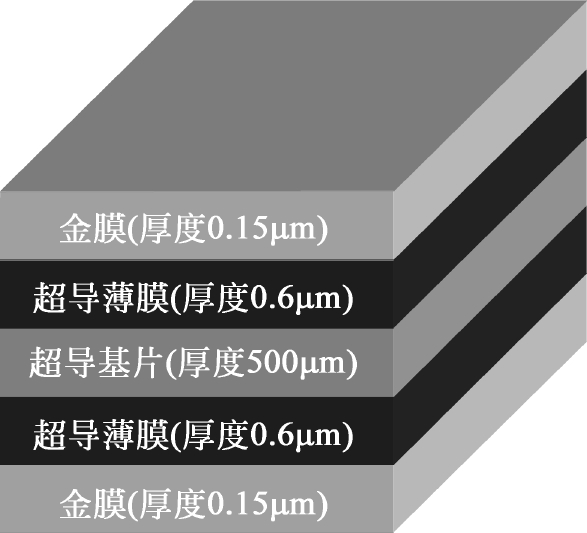

技术指标要求

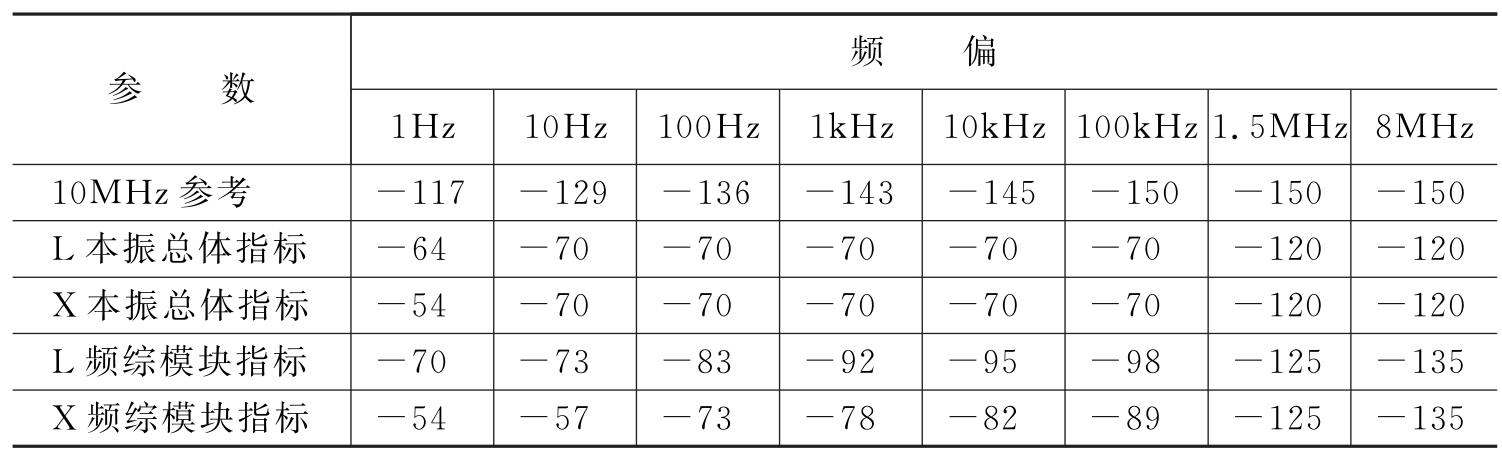

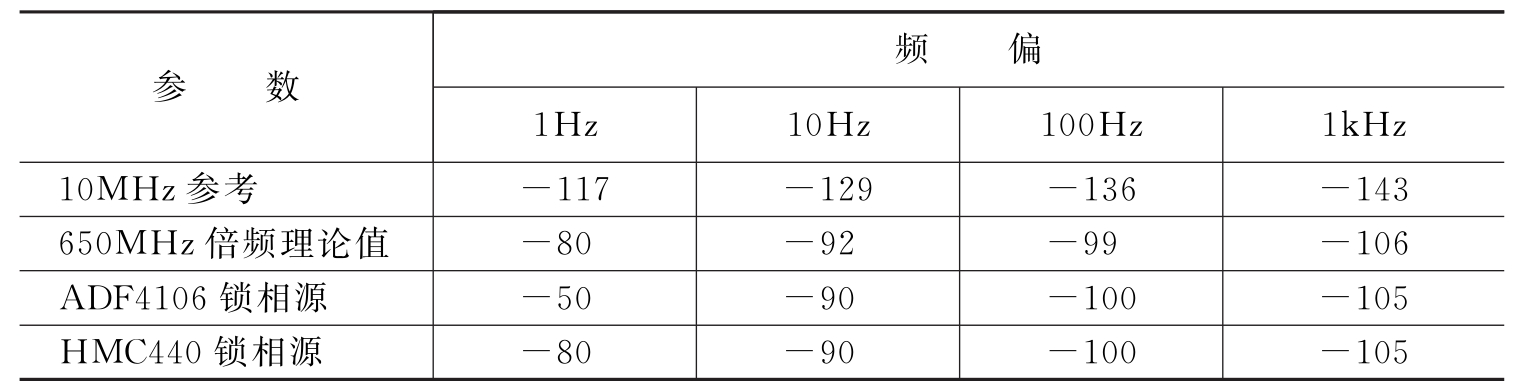

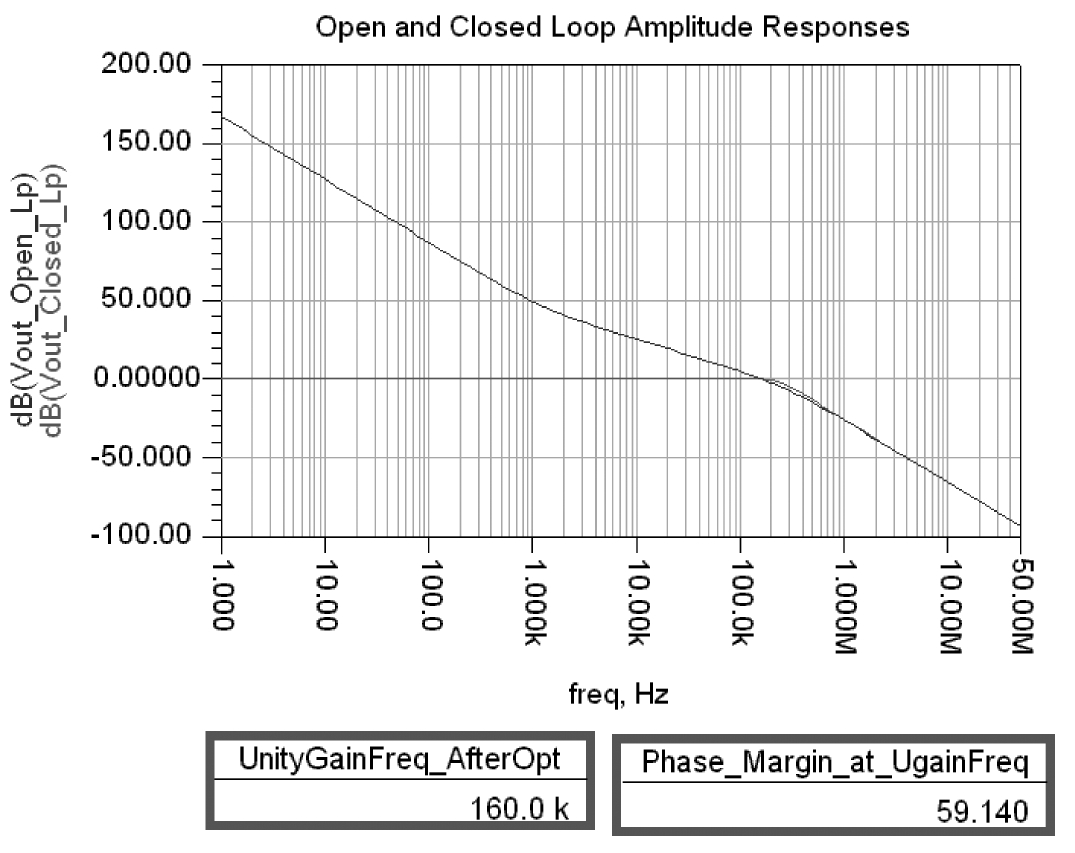

频率综合器是高频信道的重要组成部分,相比以往的测控通信系统,深空测控对频综器的要求更高,主要表现在1Hz和1.5MHz的低相噪要求,如表4-2所示。

表4-2 频综器相噪指标要求 单位:dBc/Hz

频综器相位噪声来源

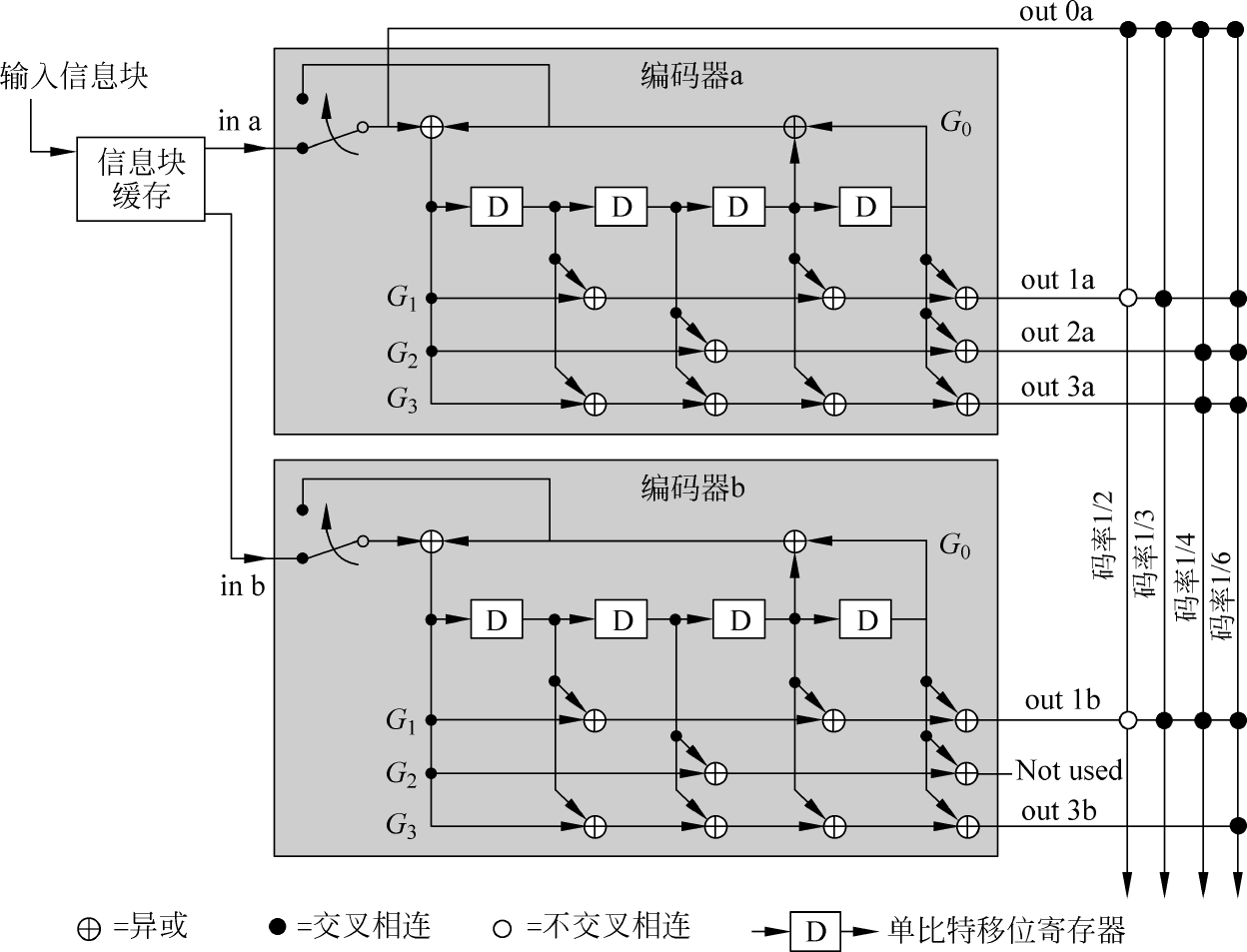

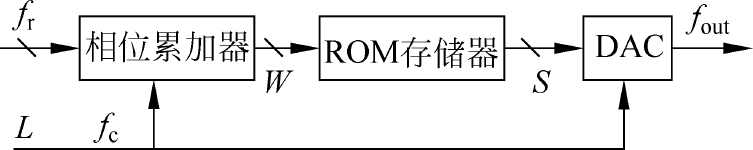

频综器主要分为5个部分,分别是:参考源倍频、参考鉴相、VCO、分频器以及DDS,其线性相位噪声模型如图4-26所示。

图4-26 线性相位噪声模型框图

各部分噪声统计独立,对各部分噪声的闭环传输函数进行分析可知:PD、DDS和参考源的噪声表现为低通特性,环路带内噪声线性相加(其中参考源噪声是倍频恶化后再线性相加),环路带外噪声受到抑制,因此这一部分噪声对环路输出的远载端相噪贡献不大;而VCO的噪声包括控制端的寄生干扰和内部噪声,表现为高通特性,环路带外噪声保持白色频谱特性,环路带内噪声受到抑制,因此这一部分噪声对环路输出的近载端相噪贡献不大。所以,环路带宽是频综器设计首先需要考虑的问题。器件手册直接提供VCO的相噪曲线,集成芯片(含鉴相、分频器等)的相噪曲线采用仿真的方法得到,工程上常取2个曲线的交点作为环路带宽的设计值,可减小VCO噪声对近载端相噪的影响,又能控制参考源等噪声对远载端相噪的影响,使频综器的相位噪声最优。DSF1的频综器设计带宽为120kHz。

环路带内噪声

鉴相器相噪基底

下行信道要求本振在1Hz相位噪声为-64dB/Hz(L频段)或-54dB/Hz(X频段),但各种型号的鉴相器在1Hz处的相噪都未明确给出。为了验证鉴相器对输出相位噪声的贡献,分别采用电流型鉴相器(ADF4106)和电压型鉴相器(HMC440)设计650MHz锁相源进行测试。相噪数据如表4-3所示,10MHz参考由晶振8607提供。

表4-3 两种鉴相器实测相噪数据对比 单位:dBc/Hz

单点频锁相源带内相噪包括参考源相噪和鉴相器相噪,参考源相噪按照20lg(倍频次数)的规律恶化。试验结果至少表明:电流型鉴相器在1Hz处的相位噪声凸显,远大于参考倍频后的相位噪声,而电压型鉴相器在1Hz处的相位噪声并不凸显。因此,下行本振采用电压型鉴相器。

鉴相器的基底相噪对输出相位噪声的贡献为

式中 LPD(f)——鉴相器的基底相噪;

fc——鉴相频率;

N——倍频次数。

利用实测相位噪声计算两种鉴相器的在1Hz处相噪基底如表4-4所示,650MHz锁相源鉴相频率为10MHz。

表4-4 两种鉴相器在1Hz处相噪基底计算结果

HMC440器件手册提供在10Hz处相位噪声为-233dBc/Hz,一般情况下认为1Hz处的相位噪声比10Hz处的相位噪声大10dB,因此-233dBc/Hz<在1Hz处鉴相基底<-187dBc/Hz。

DDS相位噪声

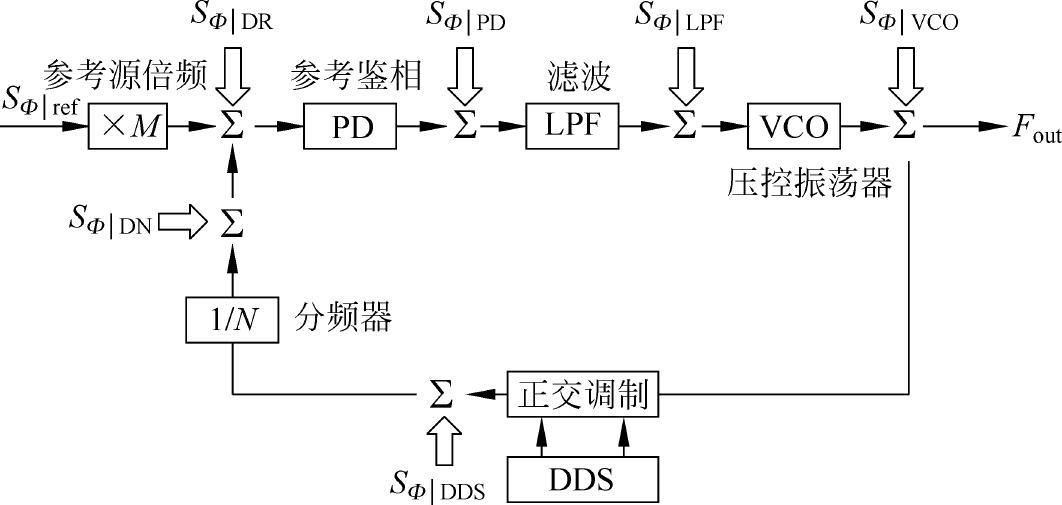

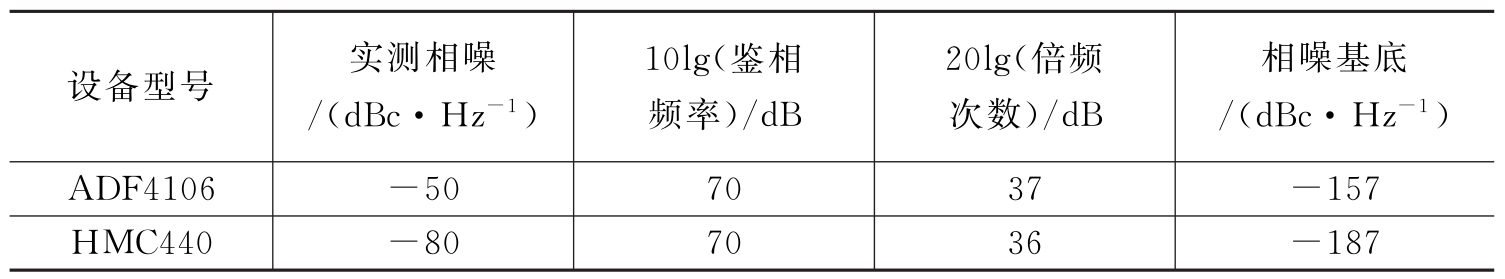

现代测控系统的频综器无一例外采用了DDS插入PLL综合设计的方法,并在此基础上结合正交调制技术,正交调制器利用2路DDS简单的相位关系就可以实现杂散信号的有效抑制,使环路的设计复杂程度大大降低。环路内插的原理如图4-27所示。

图4-27 DDS正交调制内插环路原理框图

该方法的优点在于:利用AD公司成熟的商用芯片,很容易实现DDS双路正交调制,并保持了DDS的所有特性,包括相噪和频率分辨率等,其相噪以线性相加的关系引入PLL环路;同时由于正交调制器对无用边带和本振均有一定抑制(30dBc),环路即使不加滤波器也可以正常锁定,彻底解决了DDS混频时产生的双边带杂散,降低了宽带、小步进频综器的复杂程度。DDS原理如图4-28所示。

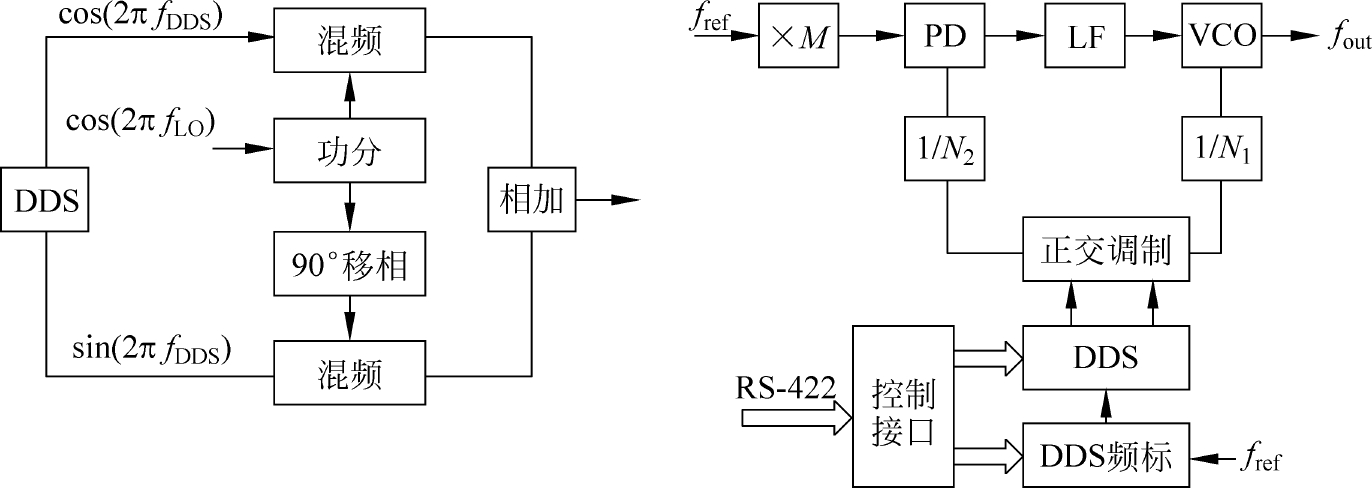

图4-28 DDS原理框图

DDS相位噪声包括累加器相位截断引入的相位噪声、ROM存储器有限字长引入的相位噪声和数模转换器(DAC)量化引入的相位噪声。DDS输出的最高频率严格限制为时钟频率的1/2,考虑到杂散因素,通常使用在时钟频率的1/4以下,因此具有分频功能。理论上,时钟相噪以分频比N优化,DDS相噪对输出相位噪声的贡献为

式中 Lc(f)——时钟相噪;

N——分频次数。

但是,实际上分频优化值比理论值小,工程上一般按照相差3dB处理。严重时,附加相位抖动完全抵消分频优化部分,甚至使DDS输出相噪差于时钟相噪。工程手册未直接提供DDS相位噪声,但仍然可以分析不同输出频率时的相噪表现,采用凸显的方法确定其相位噪声。当一款常用的DDS集成芯片的输出频率为80MHz和5MHz时,该DDS在100Hz、1kHz、10kHz和100kHz相噪数据如表4-5所示。

表4-5 DDS相噪计算结果 单位:dBc/Hz

理想情况下,如图4-11所示的300MHz时钟相噪按照DDS分频比优化。当输出频率为80MHz时,分频比相对较小,输出相噪基本体现了时钟相噪的理论变化,如式(4-3)所示。当输出频率为5MHz时,分频比相对较大,理论上将在80MHz相噪基础上继续优化24dB,但实际上优化很小,可以认为5MHz时的输出相噪即DDS贡献的相噪,因此其影响凸显。图4-11所示频综器的设计方案中,DDS的最高输出频率为60MHz,与表4-5中输出频率为80MHz时的相噪相当;方案中DDS的最低输出频率为10MHz,与表4-5中输出频率为5MHz的相噪相当。按照10dB滚降外推,1Hz、10Hz的相位噪声分别低于-104dBc/Hz和-114dBc/Hz。根据图4-11,参考源6倍频后作为DDS时钟,输出后与相同参考源经本振环PLL倍频155次后的输出正交混频,按照线性叠加原理,DDS相噪可以忽略不计。

参考源相位噪声

参考源相位噪声对输出相位噪声的贡献为

(4)环路带内噪声

DDS和PLL混合型频综器的带内相位噪声取决于鉴相器相位噪声L1(f)、DDS相位噪声L2(f)以及参考源相位噪声L3(f)(单位均为dBc/Hz)。因此在环路带内输出信号的相位噪声L(f)(dBc/Hz)可由下式得到:

如前所述,采用HMC440设计的频综器,带内在1Hz处相噪仍由参考倍频决定。

L本振环的最高输出频率为1550MHz,DDS相噪线性相加,可以忽略。频偏为1Hz时,10MHz参考源相噪为-117dBc/Hz,通过环路的锁相倍频,相噪恶化量为20lg(1550/10)=44(dB),因此输出相噪L3=-73dBc/Hz。根据表4-4所示,HMC440在1Hz处的鉴相基底小于-187dBc/Hz,则鉴相器引入的输出相噪L1=-189+10lg50+20lg(1550/50)=-80(dBc/Hz),小于参考源引入的相噪。根据第(2)点的分析可知DDS相噪L2<-104dBc/Hz。因此在1Hz处相噪由参考源决定,为-73dBc/Hz在1Hz,可以满足-70dBc/Hz的模块技术要求。

环路带外噪声

VCO产生带外噪声,其大小决定于有载QL值和各种内部噪声:

式中 F——VCO噪声系数;

K——玻尔兹曼常数;

T——绝对温度;

Ps——输出功率;

QL——有载品质因数;

fn——闪烁噪声拐角频率;

f0——载频。

根据上式可知:VCO的频带越宽,有载QL值越低,近载端相噪越差。但由于输出功率大,VCO远载端相噪反而比参考倍频的相噪低。因此,倍频后加±2.5kHz晶体滤波器抑制参考源对环路带外相位噪声的影响。

L频综合器设计

设计原理

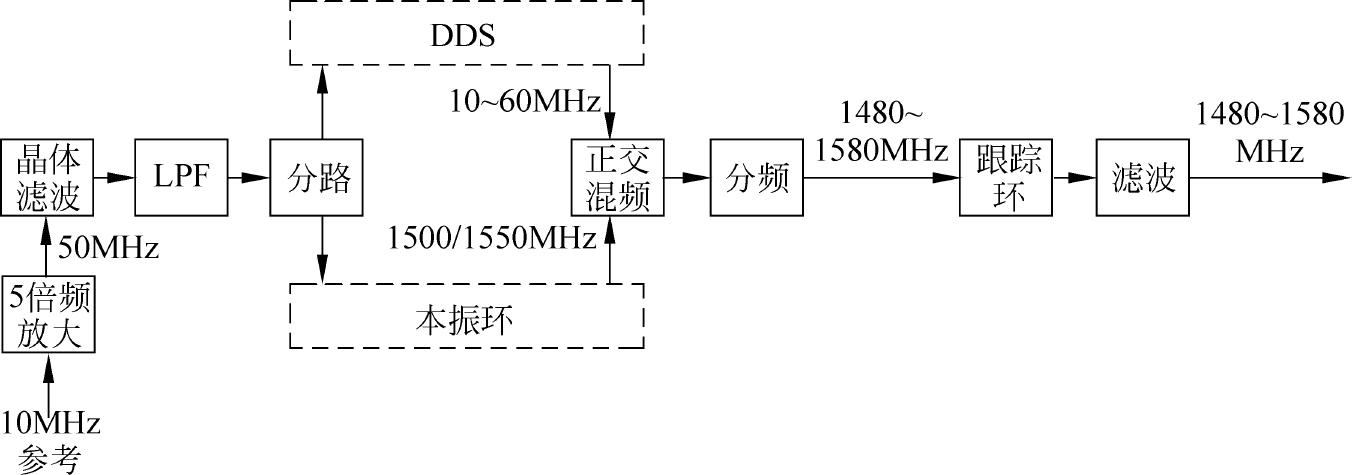

L频综器采用DDS与PLL混合设计,由DDS控制输出频率的最小间隔,如前所述,DDS由激励环路完成锁相倍频改进成内插环路的方式,避免了DDS因倍频锁相引入的相噪恶化,如图4-29所示。

图4-29 L频综器设计框图

相噪指标分析

频综器采用多种措施,改善在1Hz相噪和在1.5MHz相噪:

- 10MHz参考采用低相噪三极管倍频,提高鉴相频率到50MHz,改善集成芯片的带内相位噪声;

- 参考倍频之后加±2.5kHz的晶体滤波器,改善100kHz及更远端的相噪;

- 本振环采用窄带VCO,改善带外远端相位噪声,同时减小对带内近载端相噪的影响,程序控制1500MHz/1550MHz输出;

- 采用环路内DDS正交调制满足频综器输出频率,避免DDS倍频产生的杂散及相噪恶化等;

- 跟踪环采用窄带PLL,进一步改善带内相位噪声。

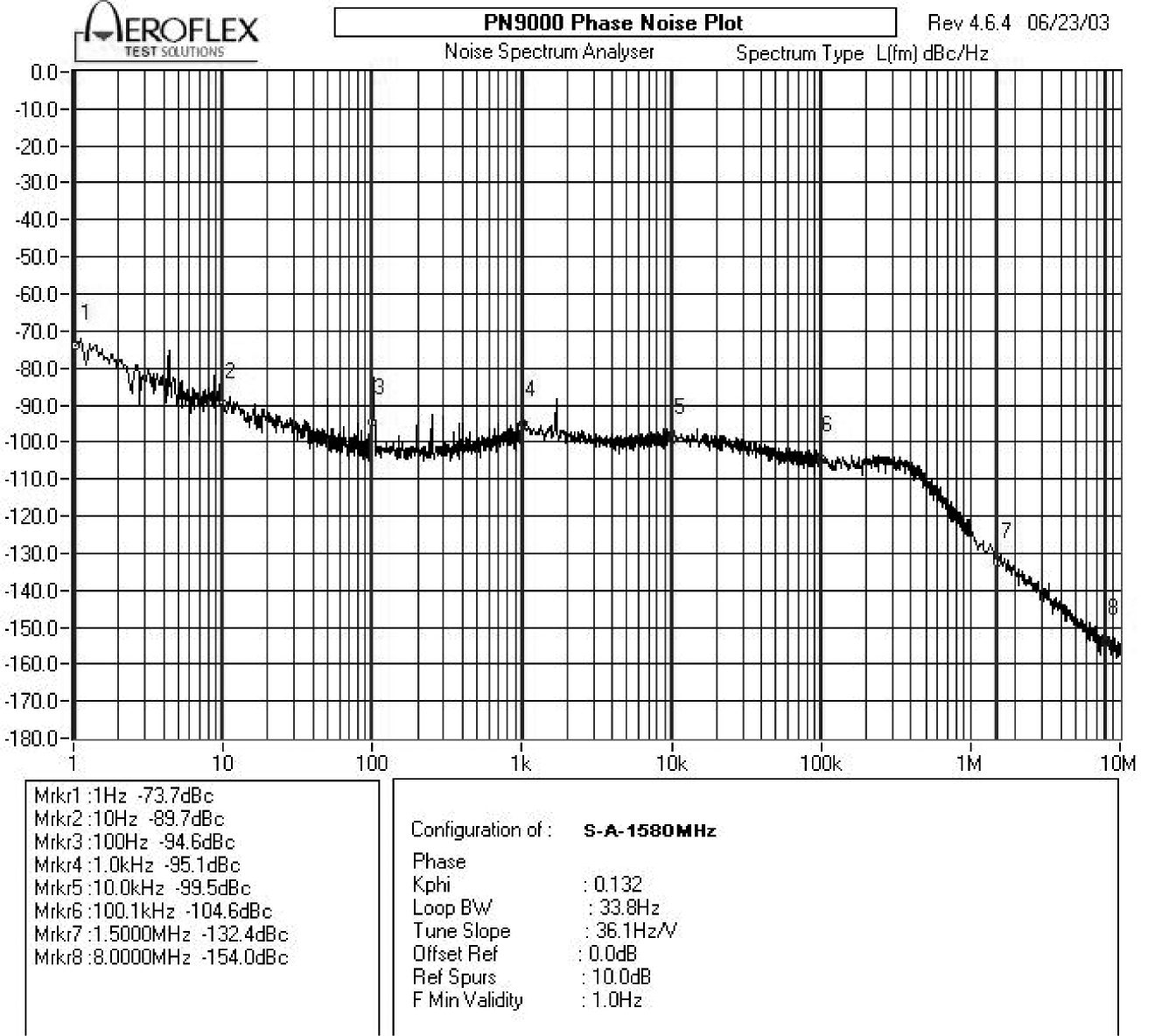

如前所述,在1Hz处近载端相噪仍主要由参考源决定,而远载端相噪主要由VCO决定。当然,如果环路带宽或环路参数设置不当,VCO相噪可能会影响近载端相噪,但通常不考虑对在1Hz相噪的影响。采用电压型鉴相器的频综器各关键点相噪如表4-6所示。

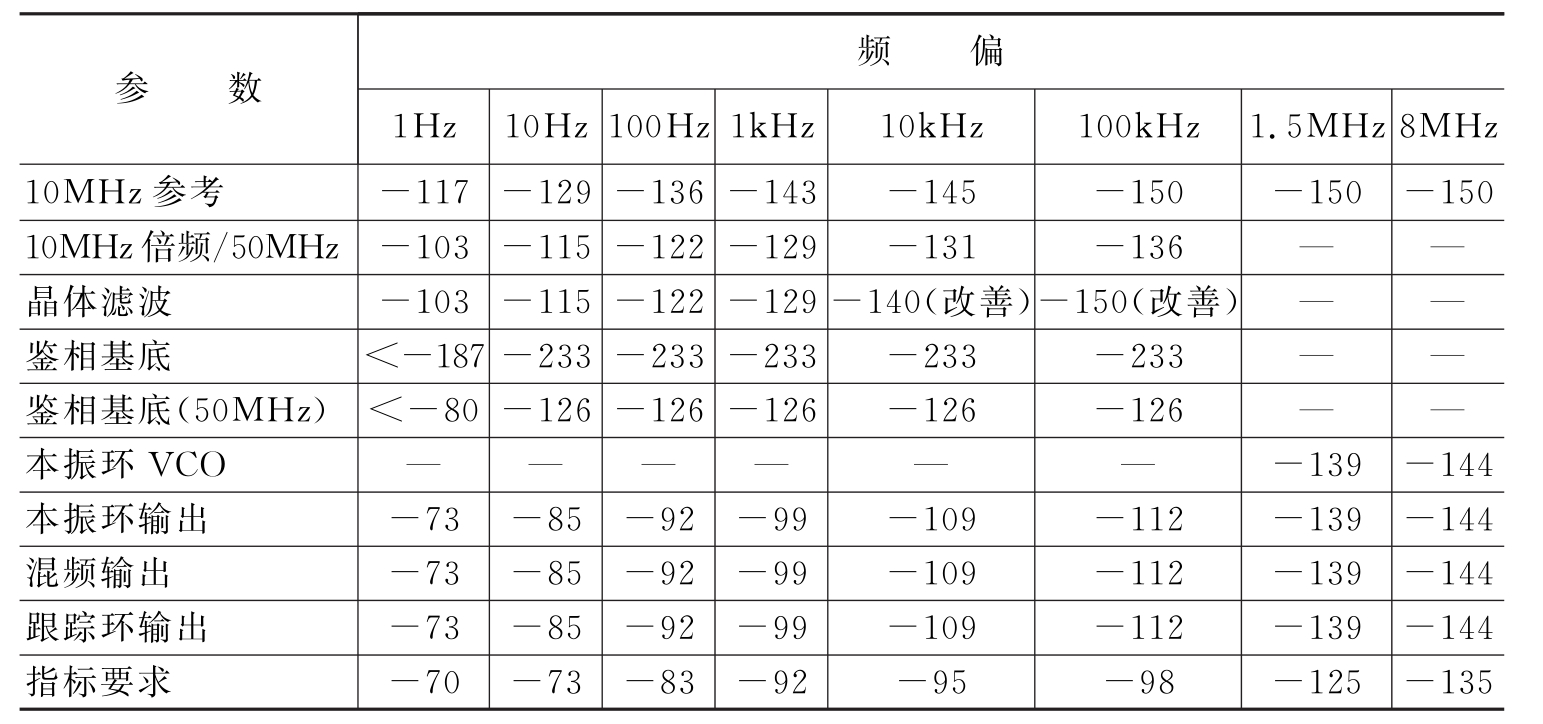

表4-6 L频综器相位噪声 单位:dBc/Hz

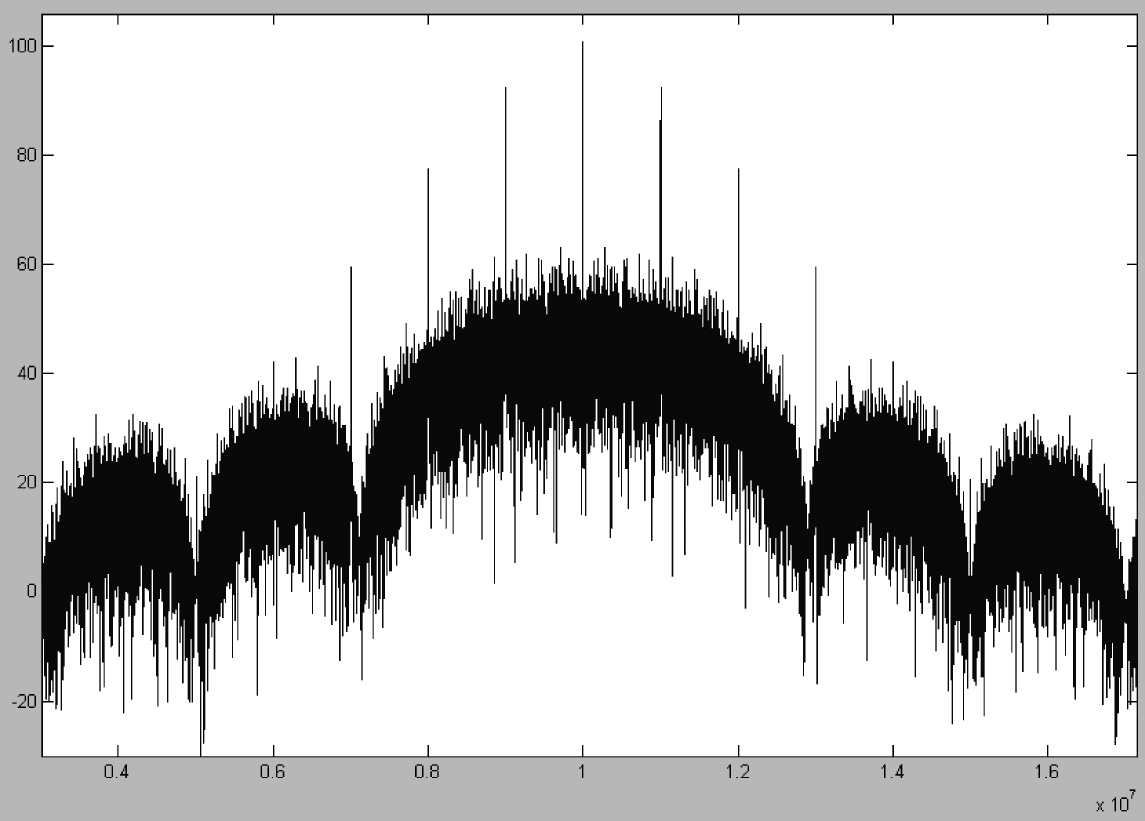

实测L频综器在1Hz的输出相噪为-73dBc/Hz,与设计值-70dBc/Hz非常接近。图4-30所示为典型测试结果,满足指标要求。

X频综器设计

设计原理

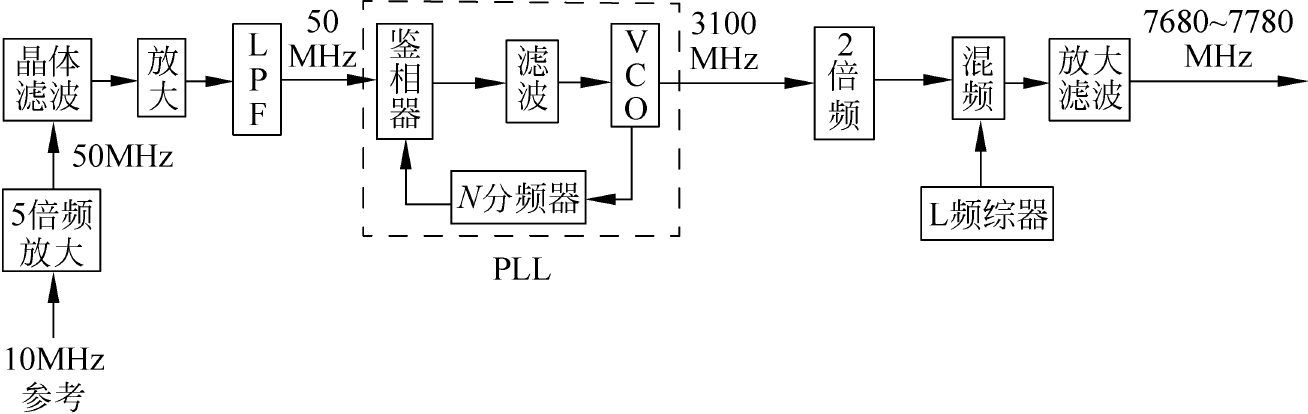

利用L频综器,与6200MHz锁相源混频,输出X频段本振信号。6200MHz单环的实现原理比较简单,由10MHz外部参考信号经倍频后激励一数字环,锁相后输出频率3100MHz,再通过2次倍频得到6200MHz,实现原理如图4-31所示。

图4-30 L频综器典型实测曲线(截屏图)

图4-31 6200MHz单环设计框图

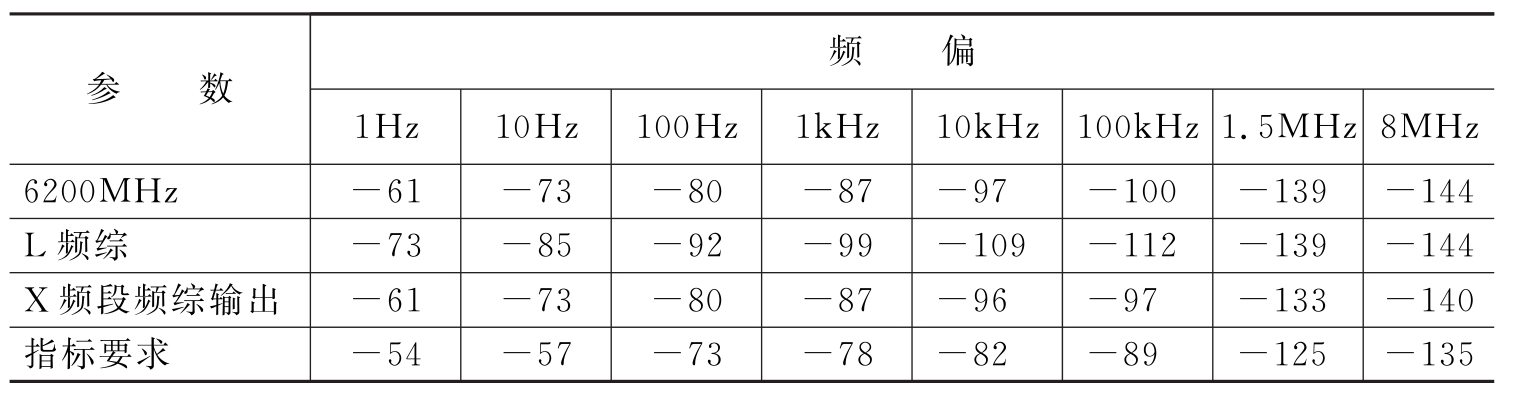

鉴相器采用Hittite公司电压型低相噪数字鉴相器HMC440,同轴介质谐振器(CRO)为定制,PLL反馈端外置二分频器,选取鉴相频率为50MHz,设计环路带宽150~200kHz,确保100kHz受带内噪声的影响,相噪满足指标要求。PLL频响特性仿真曲线如图4-32所示。

图4-32 6200MHz单环相噪仿真图(截屏图)

因为单环具有更高的倍频次数,它实际上决定了X频段频综器的输出相噪,工程采用3100MHz窄带VCO,改善远载端相噪,再二次倍频输出6200MHz,采用电压型鉴相器,器件手册直接提供带内在10Hz以上的鉴相基底为-233dBc/Hz。根据前述实测数据,在1Hz的鉴相基底为-233~-187dBc/Hz,单环鉴相频率为50MHz,输出频率为6200MHz,因此,归一化相噪基底恶化量为113dB,实际上各关键点相噪如表4-7所示。

表4-7 6200MHz单环相位噪声 单位:dBc/Hz

本振输出信号采用6200MHz点频信号与L频段频综器混频得到,根据其相噪指标可以得到最终输出信号的相噪指标,见表4-8。

表4-8 X频综器相位噪声 单位:dBc/Hz

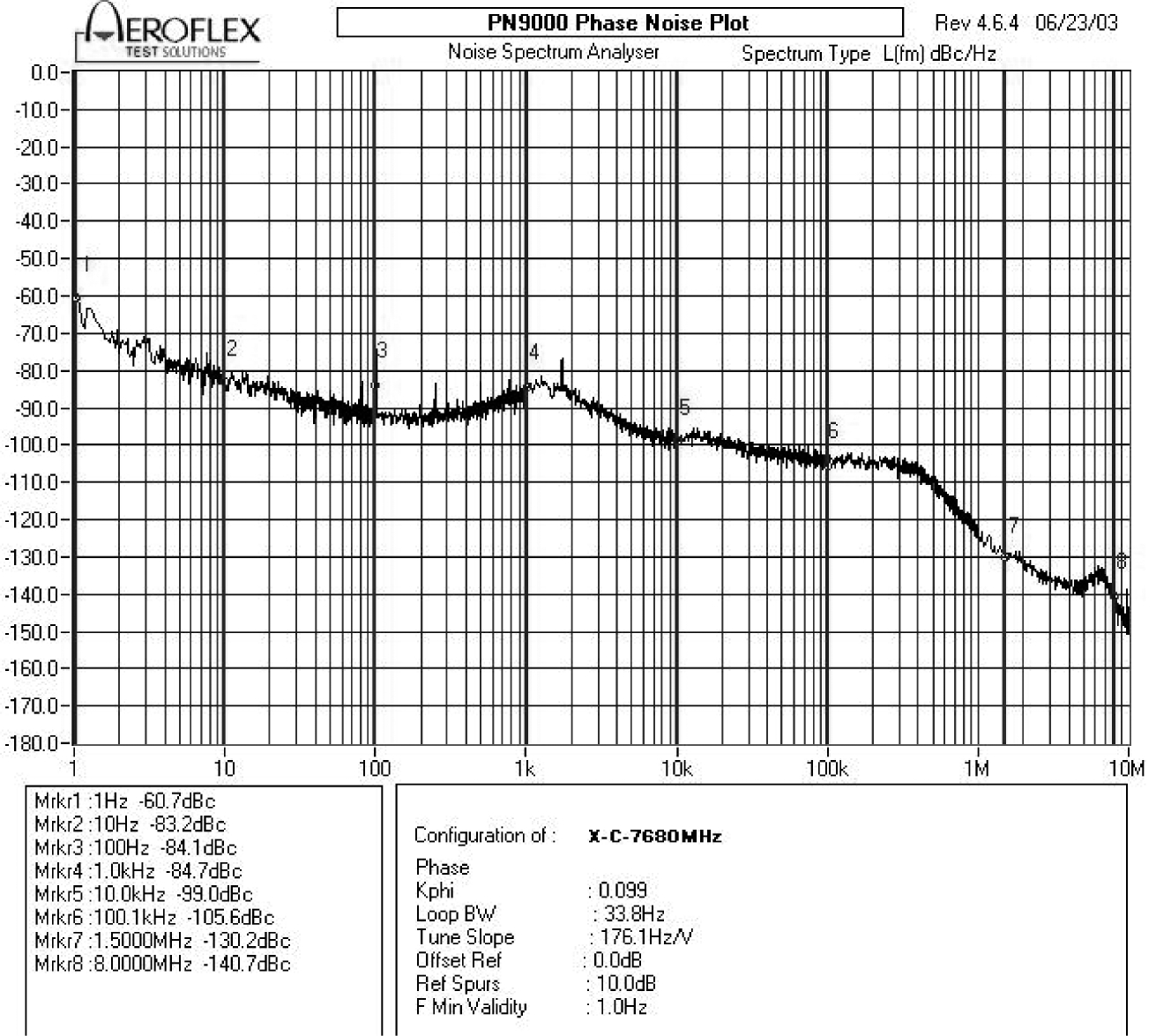

实测X频综器在1Hz输出相噪为-65dBc/Hz,与设计值-61dBc/Hz非常接近。图4-33所示为典型测试结果,满足指标要求。

图4-33 X频综器典型实测曲线图(截屏图)

杂散指标分析

为满足频综器低杂散的要求,除了不对DDS进行倍频处理外,采用的主要措施包括:

- 由于每增加1b相位截断位数,可使输出信号的杂散降低6dB,因此选用相位截断位数高达17b的DDS器件,以降低相位截断引起的杂散;

- 选用时钟频率较高的DDS器件,使输出信号单个杂散能量减小,且远离信号频率;

- 在电路设计中,对电源和数字电路进行有效的去耦滤波,分为数字接地和模拟接地,使用大面积接地等方法都减小了其他杂散。

由于频综器的输出即为锁相环的输出,锁相环对输出频谱有窄带滤波作用,截止频率等效为环路带宽,而环路的鉴相参考频率高达50MHz,远大于环路带宽,对鉴相参考频率调频杂散的抑制容易满足要求,故输出杂散主要由DDS提供。本方案采用的DDS为AD9852,根据手册提供的参数,在DDS输出频率为41MHz时,频偏±250kHz内的杂散抑制为-82dBc。由于DDS内插环路,没有倍频,故DDS对频综的杂散贡献就是-82dBc,满足-65dBc指标要求。

频率步进分析

当环路锁定时,频综器的输出频率为fout=fref×6×(24~26)+fDDS,其中,fref为参考频率,fDDS为DDS输出频率,由频率控制字和时钟决定fDDS=Kfclk/248。本方案采用DDS相位截断位数为48b,时钟频率为10MHz参考信号倍频为300MHz,因此DDS的最小频率间隔ΔfDDS为

由于采用DDS内插锁相环路的方案,其最小频率间隔即为频综器的步进,满足100Hz的使用要求。