原理简述

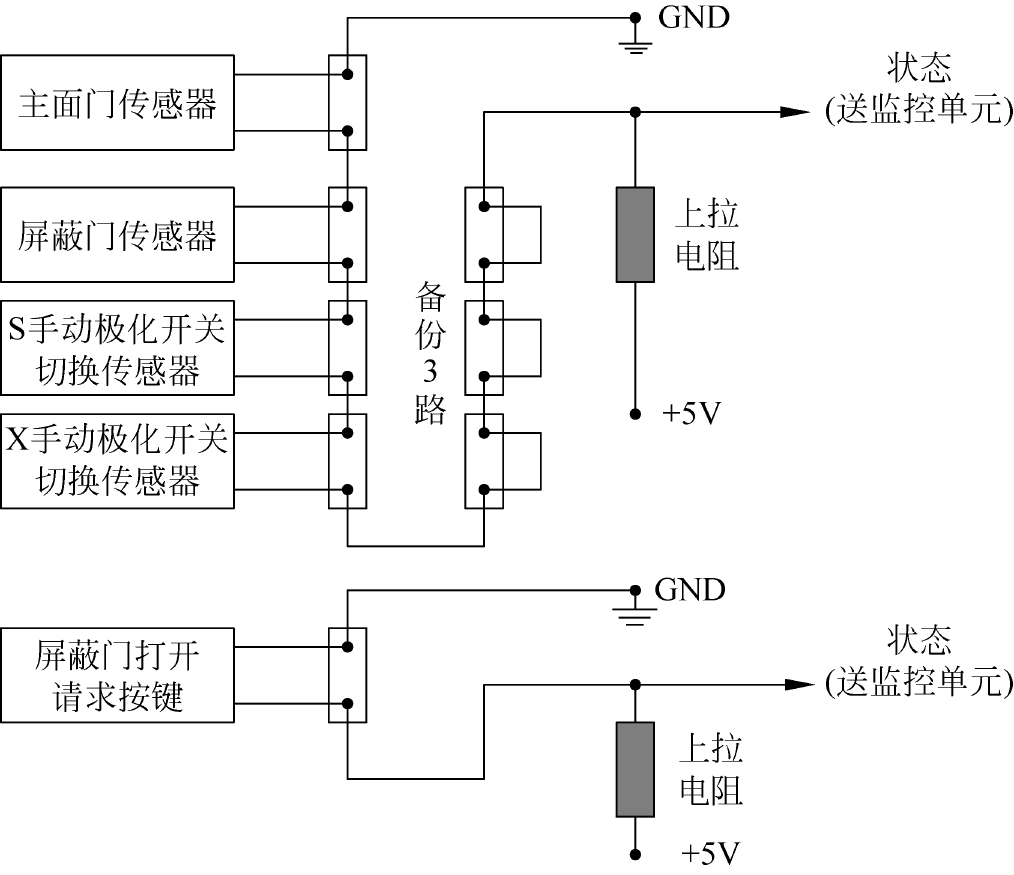

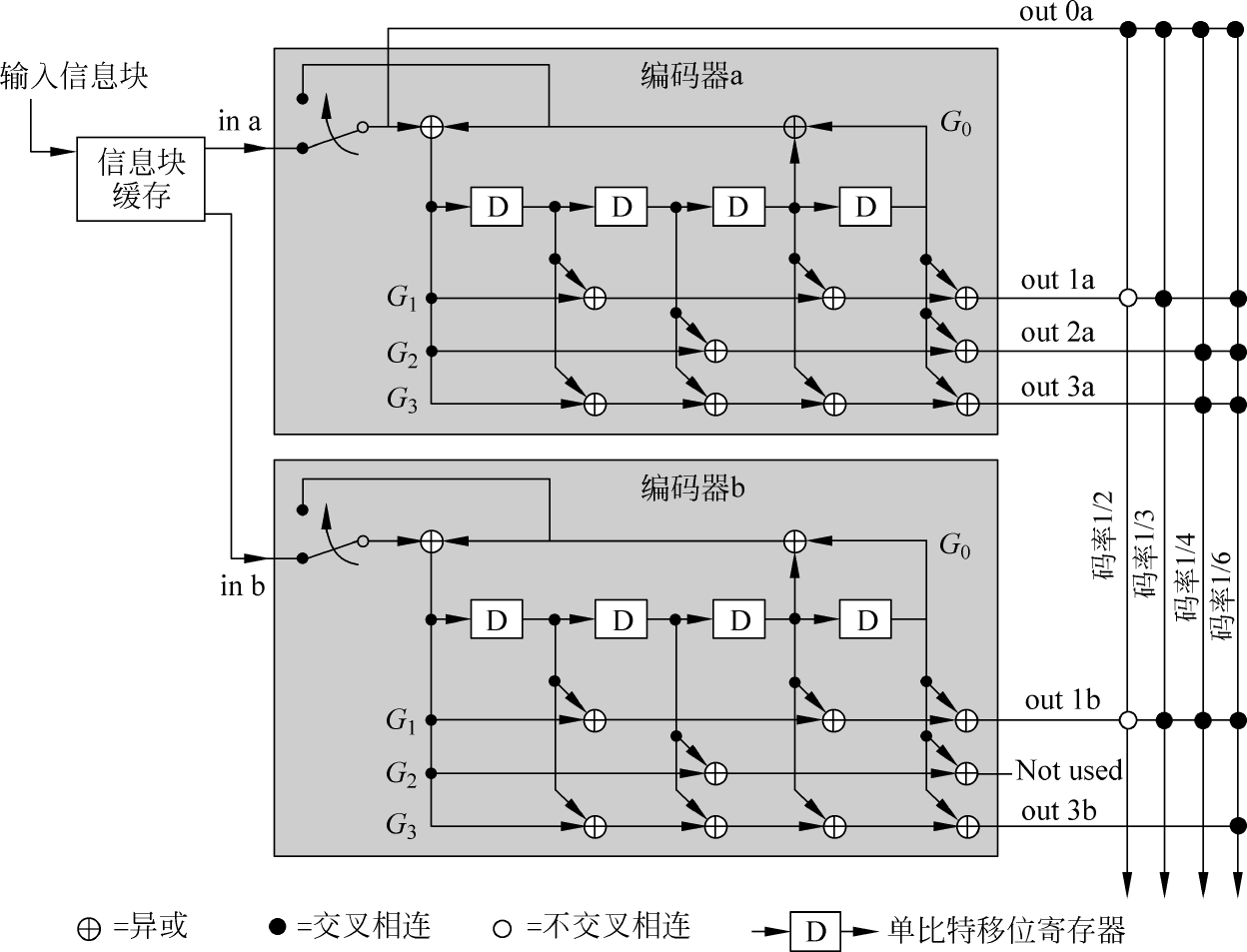

本振模块使用单环实现(见图3-12)。用倍频电路将10MHz倍频到40MHz,40MHz滤波器采用晶体滤波器改善40MHz远载端相噪。鉴相器HMC440单环合成,鉴相基底-223dBc/Hz,鉴相频率为40MHz,倍频次数7次。

图3-12 本振模块原理框图

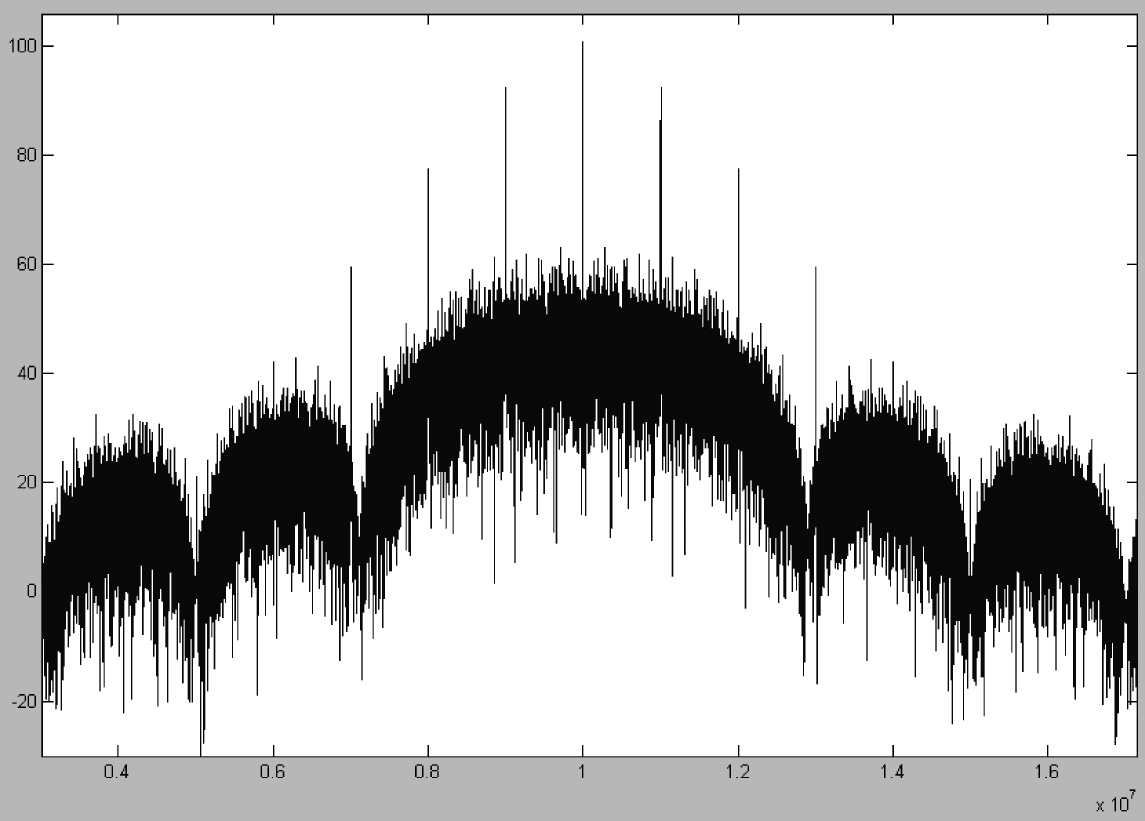

相噪分析计算

环路带宽内的相噪取决于输入参考源的相噪和锁相环(PLL)自身的噪声基底,DDS的相噪可忽略不计。环路带宽外的相噪取决于压控振荡器(VCO)相噪。在PLL环路带宽内,参考信号和鉴相器引入的噪声由如下计算得到:

参考信号的相位噪声对输出信号相噪的贡献:

式中 Lr(f)——输入参考的相位噪声(dBc/Hz)。

鉴相器的基底相噪对输出信号相噪的贡献:

式中 LPD(f)——鉴相器的基底相噪(dBc/Hz);

Fc——鉴相频率。

因此,在环路带内输出信号的相位噪声L(f)(dBc/Hz)可由下式得到:

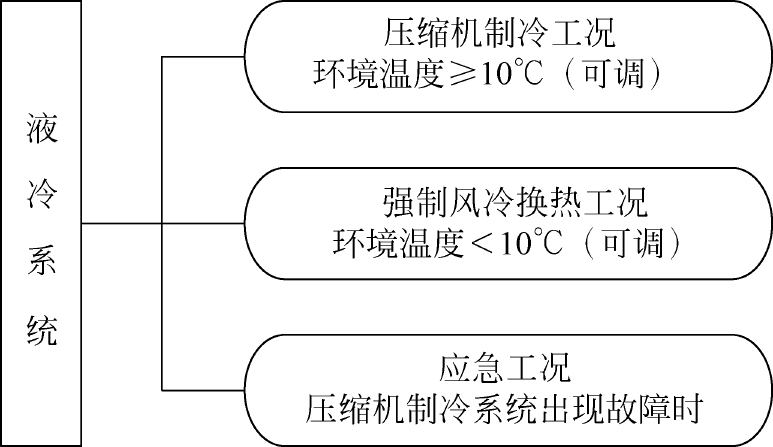

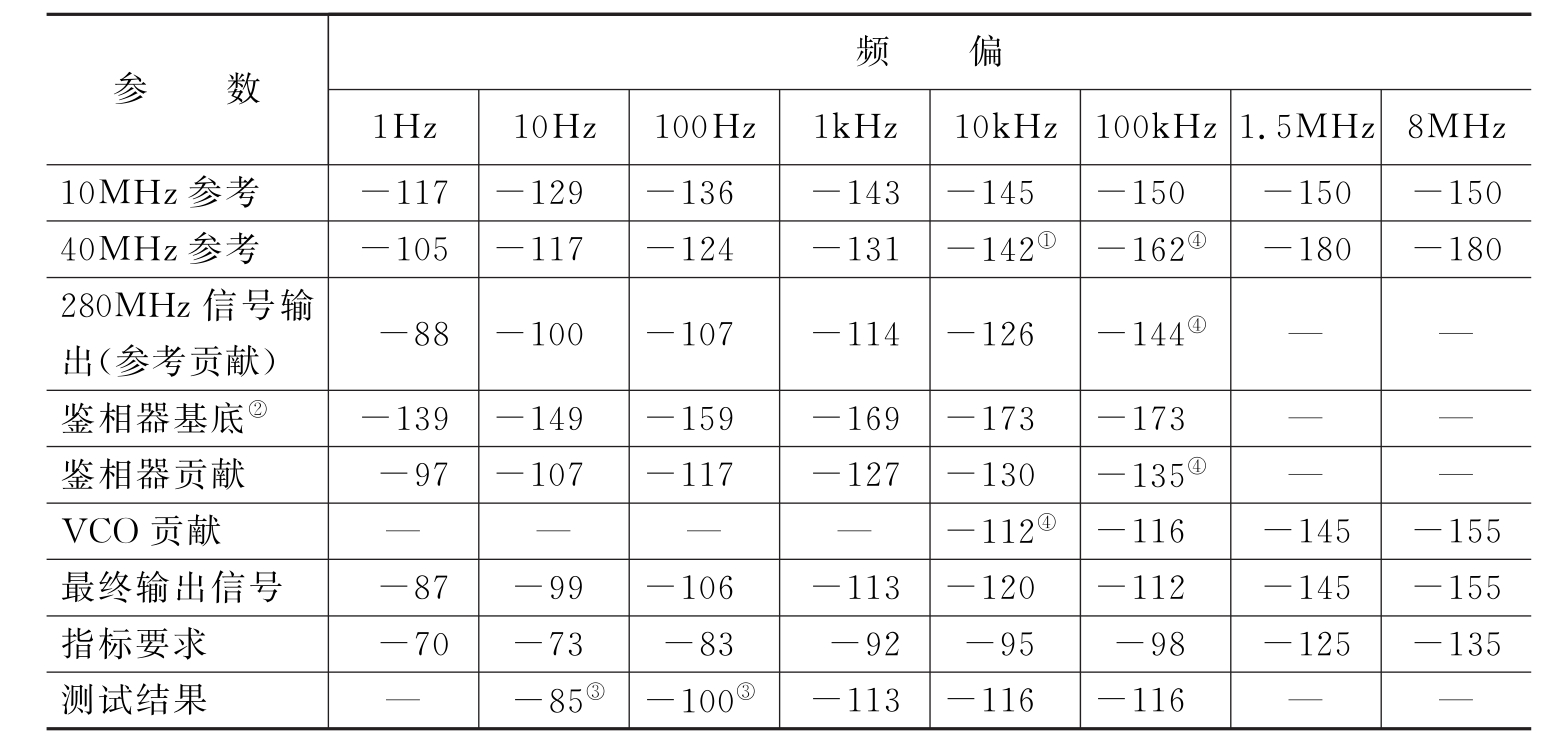

10MHz参考在1kHz处的相噪按-143dBc/Hz,VCO 10kHz处相噪为-112dBc/Hz,环路带宽约为70kHz,鉴相器基底1/F拐点频率为100kHz,倍频恶化17dB。40MHz晶体滤波器对10kHz以外相噪改善在14dB以上,则输出的相噪计算如表3-1所示。

表3-1 本振相噪指标分析表 单位:dBc/Hz

注:①晶体滤波器对10kHz以外相噪有改善;

②近载端相噪按1/F恶化;

③仪器噪底值;

④环路改善100kHz及100kHz以外相噪。

谐波抑制

谐波抑制靠输出腔体滤波器保证,实际谐波抑制大于60dB。

杂波计算

杂散主要是鉴相泄漏,结合工程经验,在环路为70kHz、倍频恶化17dB(理论值12dB,倍频损失5dB)时,40MHz鉴相泄漏其抑制度大于-80dBc。